# 3 Project Plan

#### 3.1 PROJECT MANAGEMENT/TRACKING PROCEDURES

We are doing a combination of waterfall and agile management style. Since our project has some necessary components, pre-defined development checkpoints come about through those components. These checkpoints follow a more waterfall approach, however we are able to pursue these checkpoints with whatever strategy most effectively achieves them, which is more in line with the agile approach.

We are tracking our progress with photo documentation of our work as we go, so that we have evidence of what we have done to compare back to.

## 3.2 TASK DECOMPOSITION

Our project breaks down into a few key components- ADC, wi-fi connection, and display. Of these, the most complicated and first component that must be developed is the ADC. The ADC needs to receive the analog input, run a fast enough clock for itself, the amplifier, and the wi-fi controller, and convert the input to a displayable digital signal. For testing purposes, it is more beneficial to create a framework of a display here, and develop it more so later down the line. This way, we can tell if the ADC is functioning as intended using a wired connection. The wi-fi connection comes next, configuring a separate microcontroller with wi-fi capabilities to receive and transmit the output of the ADC. Finally, we will set up a display so that the initial signal received by the ADC is readable by humans in a user-friendly interface.

#### 3.3 PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

The major milestones for this project are written out as follows. We will finalize the ADC code for the STM microcontroller, work with the STM 32H750 with a better internal clock to get the correct sampling rate needed. After that is complete we move onto the ESP32 which has wifi capabilities and then transmit the data to a display. We will know that the STM blue pill code works by us being able to see a sinusoidal wave produced upon a screen with a code connection. This will also be verified by us changing the input into the device so we can see that the device is showing us the correct value for the input. After that is complete, we will then move onto the STM 32H750, and to know this works, we will have to have the sample rate high enough and that shows upon the wired display with the accuracy we need. This will also be tested and cleared when we can see the system outputs the signal we input with the correct frequency. Then we will move onto the wifi portion, which is verified by seeing the data show up on a screen when no cable is used and that it is consistent, with a 80% rate for the screen showing and the connection made. The final step in this is the display and the proper graphs. We will deem this a success once we see the data is correct from the source as well as the graph is able to show the full, detailed and accurate picture.

#### 3.4 PROJECT TIMELINE/SCHEDULE

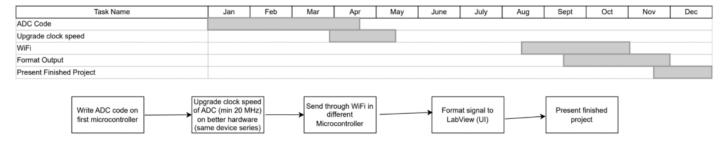

# **Gantt Chart**

This Gantt chart outlines the timeline for completing a project involving ADC code development, clock speed upgrades, Wi-Fi integration, and LabView data formatting. The tasks are scheduled throughout the year, with the main phases starting with writing the ADC code and then upgrading the clock speed in April-May. Wi-Fi setup will take place in August-October while formatting the output signal in LabView is scheduled for September-December. A final presentation of the completed project is scheduled for December. Each task is linked to the next to ensure smooth project completion.

#### 3.5 RISKS AND RISK MANAGEMENT/MITIGATION

In the project, potential risks include hardware component compatibility issues, insufficient Wi-Fi transmission stability, and substandard ADC system performance. We can mitigate these risks by selecting higher-quality components, optimizing coding, or performing multiple tests. We consider purchasing off-the-shelf modules to implement the functions for possible high-cost tasks or adjusting the design to reduce development costs. In addition, agile methods will help us evaluate and manage risks in each sprint to ensure that the project proceeds as planned. For the wireless data acquisition (wDAQ) system project, agile methods mean gradually developing and testing the system's functions (such as ADC acquisition, Wi-Fi communication, etc.) through each sprint cycle and making timely adjustments based on test results and team feedback during the process, thereby reducing the risk of project failure and improving the quality of the final delivery.

#### 3.6 PERSONNEL EFFORT REQUIREMENTS

| Task                                                            | Hours |

|-----------------------------------------------------------------|-------|

| Coding STM microcontroller                                      | 10-20 |

| Coding ESP Microcontroller                                      | 1-5   |

| PCB board design, improving amplifier and other potential tasks | 5     |

| Testing/Prototyping/integrating system                          | 10    |

Coding the STM is the most difficult and time consuming part of this project. Learning the syntax and other differences of the STM takes a decent amount of time. Additionally, troubleshooting more rare and smaller problems has also proven quite troublesome. We expect the ESP microcontroller coding to be significantly easier as we are just using it to transmit the signal, although getting it to use STM's clock could prove difficult. Other tasks like designing the PCB board for the final design should not be too time consuming. Integrating all the different parts and performing comprehensive testing will likely be a time consuming ordeal. We need to make sure the waveform is accurate. It's essential for us to do this part right, as the whole project is centered around moving and displaying data.

## 3.7 OTHER RESOURCE REQUIREMENTS

The major resource we will need to complete the project will be the aid of our advisor and the help of github and other websites on the coding portion. That is a difficult task and we will need to learn a lot for this to work. Other resources are the boards themselves along with access to the lab so we can run tests, both of which are being provided by the advisor. The last resource is just time to work on the project and be able to complete the steps in a timely manner.